# LA3000

# 2-in-1 Analyzer (Logic & Protocol)

#### Hardware

- PC-based

- 68 / 136 channels

- USB3.0 interface

- 12V power

- 4GB total memory

- Stackable with a DSO to form as an MSO

- Protocol Analyzer: I2C, SD3.0, SPI, UART, ...

- Logic Analyzer: Logic triggers, Protocol triggers/decodes

- 4GHz timing analysis, 250MHz state analysis

# Protocol Analyzer

Real time display

I2C, SD 3.0, SPI, UART,...

Filter

Hardware filter to save more needed data

- Search

Search data while capturing data

- Trigger

Hardware trigger for command or data

- Waveforms

Display waveforms after capture stopped

# Logic Analyzer

- High sample rate4GHz timing analysis

- Deep memory

4GB RAM to log very long time data

- Active probe

Good impedance and 75cm long for easy setup

- Powerful triggers

Logic triggers, flow-chart bus triggers

- Many bus decodes

80+ bus decodes with waveforms

- Mixed signals

Stackable with a DSO to capture and display digital and analog waveforms

| Ch | Memory |

|----|--------|

| 64 | 500Mb  |

| 32 | 1Gb    |

| 16 | 2Gb    |

| 8  | 4Gb    |

| 4  | 8Gb    |

| 2  | 16Gb   |

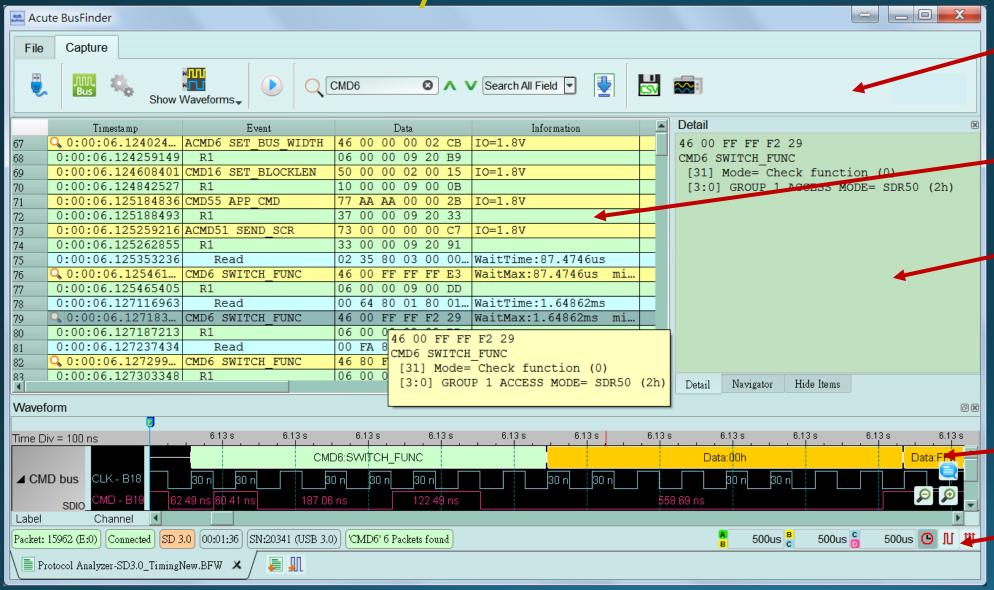

### Protocol Analyzer

Tool bar

Report window

**Details/Statistics**

Waveform window

Status bar

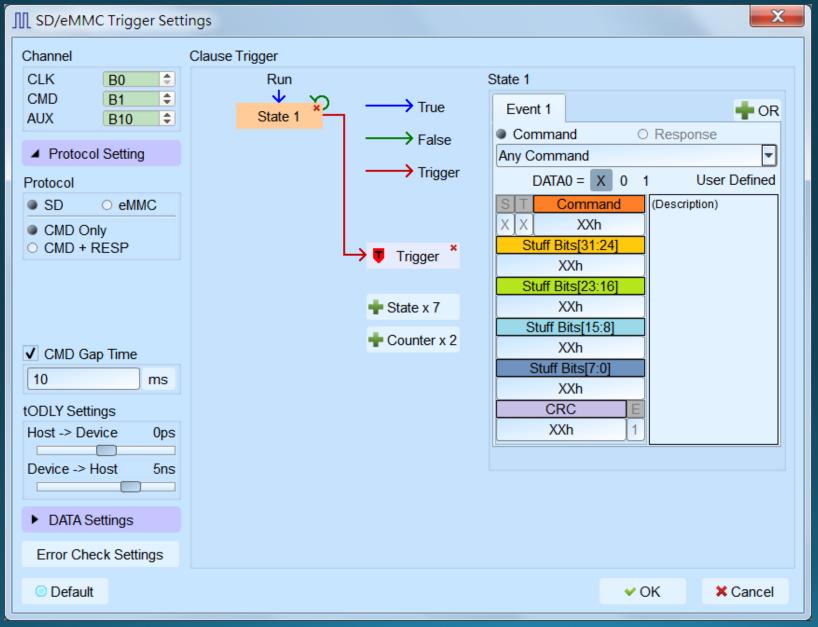

## Protocol Settings

Default

X **Protocol Settings** eMMC 5.1 Sample Rate 2.4 GHz Filter I2C Filter condition NAND Flash Primary Protocol Analyzer Data Length > 512 bytes SD 3.0 **Protocol** SD 4.0 O SD 4 Probe Trigger on CMD/DATA SD 3 Probe ...... VDD Drop CMD Trigger event O DATA Custom SD3.0 CRC16 error End bit error CRC7 error Probe Secondary Protocol Analyzer or I/O Option NAND Flash NAND channel DDR mode **Tuning settings** Protocol option O I/O 512 Block size bytes VDD detect channel A0 O A1 **▼** bit Bus width

✓ OK

**X** Cancel

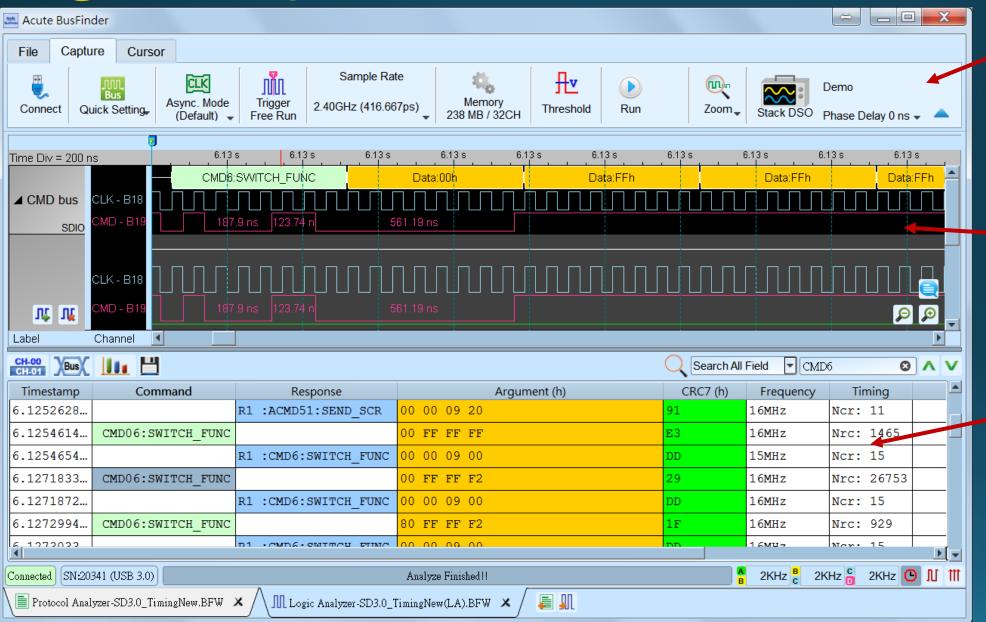

## Logic Analyzer (SD 3.0)

Tool bar

Waveform window

Report window

# Logic Analyzer-Trigger Settings